# (Beam Diagnostics) Data Acquisition

#### Marek GASIOR, CERN, AB/BDI

email: marek.gasior@cern.ch

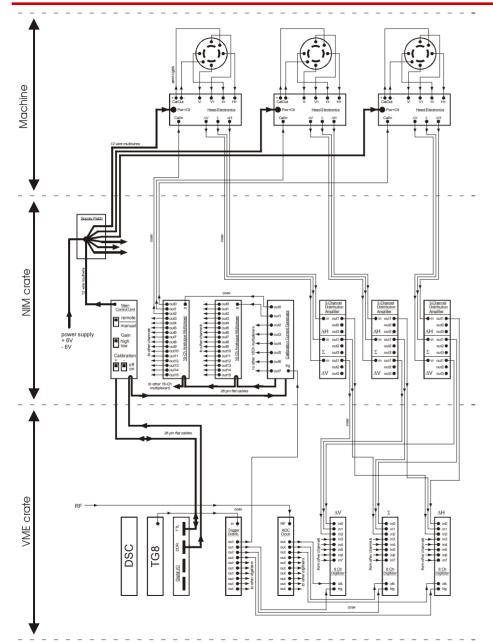

- BPM system layout

- System components

- Testing & Calibrating

- ADC modules

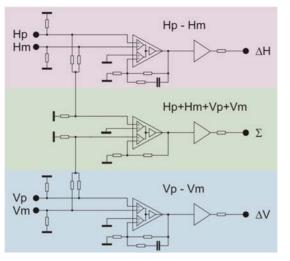

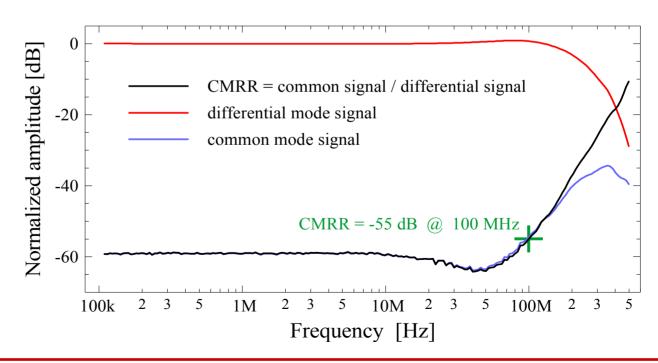

- The module produces  $\Delta$  and  $\Sigma$  signals

- Δ high cut-off frequency is about 200 MHz, for Σ signal - 250 MHz

- The CMRR at 100 MHz is as high as 55 dB

- △ signal cable lengths have to be matched within 1.6 ps, (i.e. within some 0.3 mm) to have deterioration of the CMRR from their length difference below -60 dB at 100 MHz

- Once the ∆ signals are made, it is enough to have the long cables going to the equipment room matched within 0.5 ns (a factor of 300 less than for the cables pick-up - hybrid )

M. Gasior, CERN

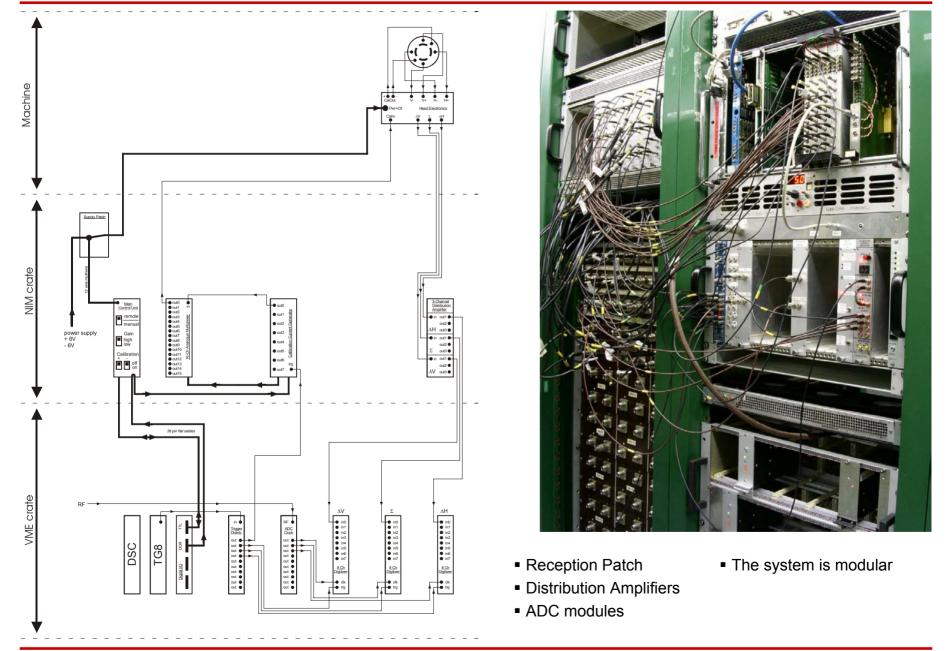

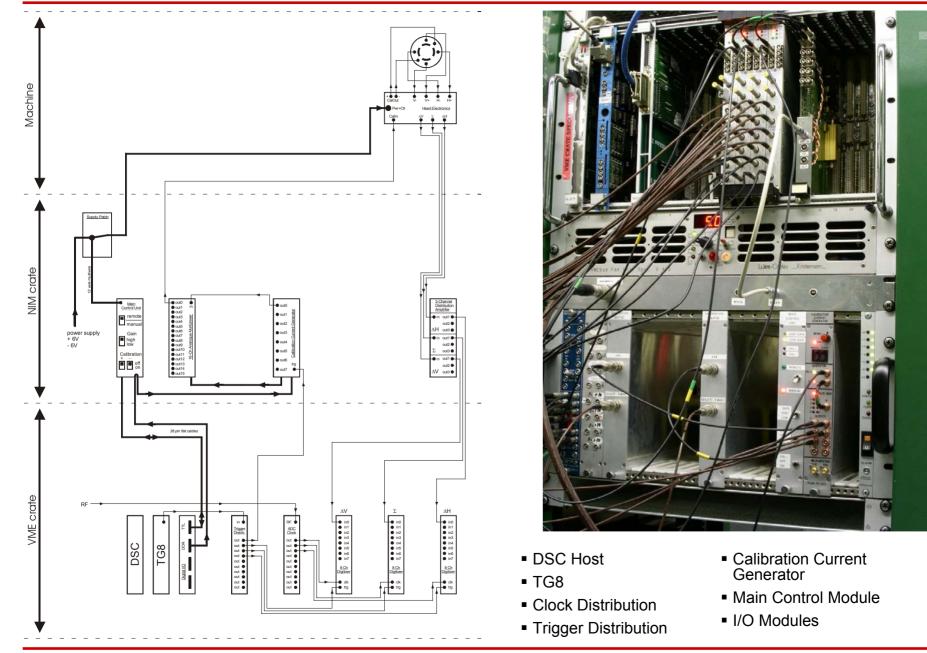

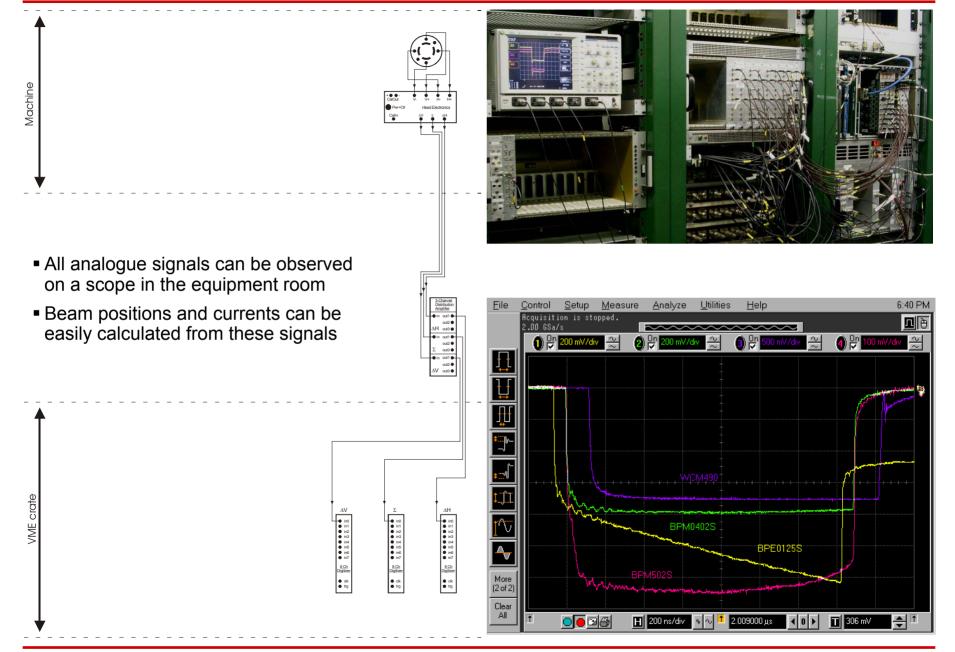

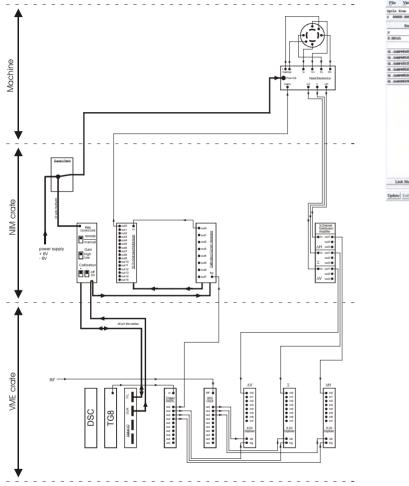

## **BPM System Layout – In the Equipment Room**

### **BPM System Layout – In the Equipment Room**

M. Gasior, CERN

(Beam Diagnostics) Data Acquisition

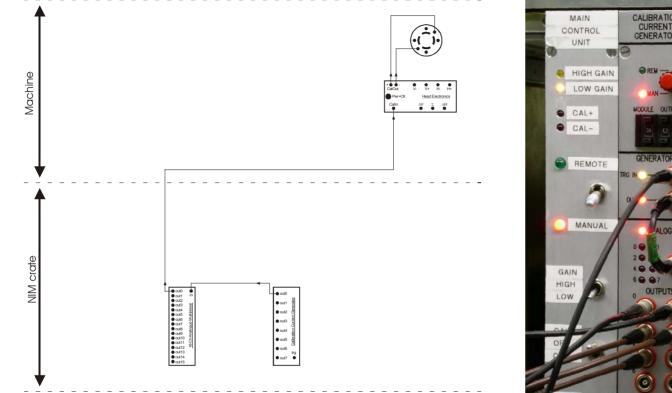

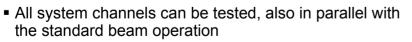

## **BPM System Layout – Testing & Calibration**

- The CCG is used to calibrate the pick-ups for the beam intensity measurement

- There is only one CCG for all pick-ups to have always EXACTLY the same pulse amplitude, the pulses are switched by analogue multiplexers

- The Calibration Current Generator (CCG) delivers current pulses of 300 mA  $\pm$  0.1%

- The pulse length is 1.5 μs (testing) and 150 μs (for calibration to reveal the pick-up signal droops)

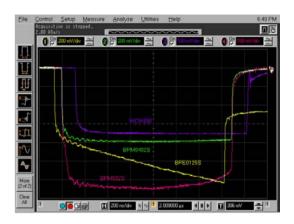

### **BPM System Layout – Scope Observation**

#### **Systems**

#### BPEs, BPMs, BPRs, WCMs

## **RF** Equipment

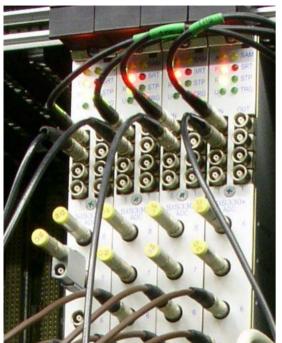

- ADC modules are of the same type for all instrumentation equipments

- Standard acquisition crate contains:

- host

- TG8 timing module

- ADC modules

- ADC clock distribution

- ADC trigger distribution

- All ADCs work with the same clock of 96 MHz (5\*19.2) derived from the RF

- Each sub-system has its own trigger

- Within one sub-system all ADC modules use one trigger

- The ADC clock and trigger inputs have 50 Ω impedance, so the signals are actively distributed to all modules

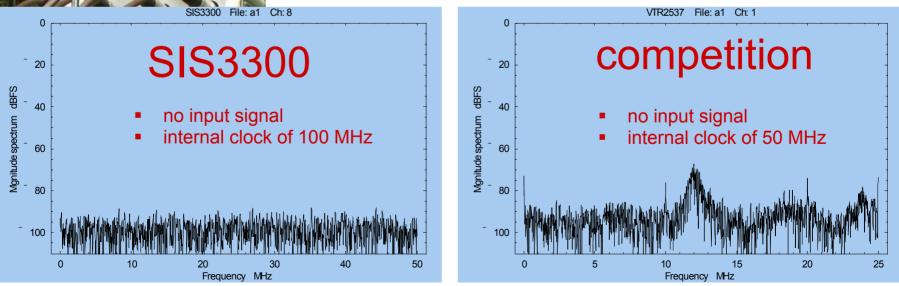

- 12 –bit, 100 MHz, 8 channel

- Memory: 256 k samples / channel

- Each module starts acquisitions a programmed number of clock ticks after the hardware trigger and stops automatically after the desired number of samples is stored

- Multi-event operation is used: a certain number of events is stored in the memory one after the other (in our case each beam pulse) and transferred at the end of the cycle (cycles of 1.2 s)

- The modules run in the dual bank memory scheme: new data is acquired (to memory bank A) while data from the previous cycle is being transferred (from memory bank B)

- The modules have many other nice things (as averaging, special trigger modes) which we do not use (for the time being)

- The modules have very good noise / interference performance

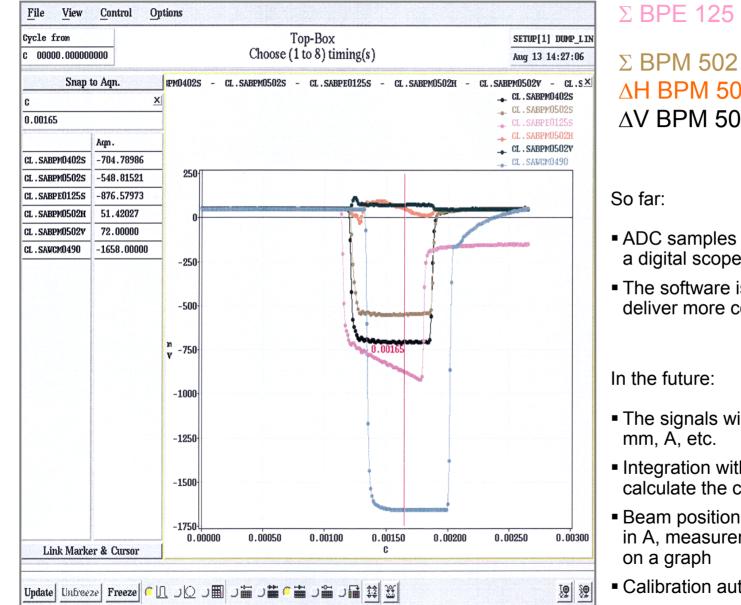

Σ BPM 502 **AH BPM 502 AV BPM 502**

WCM 0490

Σ BPM 402

#### So far:

- ADC samples were displayed as on a digital scope

- The software is being developed to deliver more complete data

#### In the future:

- The signals will be displayed in mm. A. etc.

- Integration within a given window to calculate the charge

- Beam position in mm, beam current in A, measurements in a table and on a graph

- Calibration automated

- The beam diagnostic data acquisition was successfully used to commission the machine

- Simplicity and flexibility were very important

- Scope observation was very useful

- Testing and calibration capabilities were much appreciated (by the operation as well as the HW specialists)

- In the future the system modularity will be beneficial

- The system software will still be developed

Ups...